Sep 19, 2018 原创文章

CUDA并行编程学习(1)-- 现代GPU的体系结构

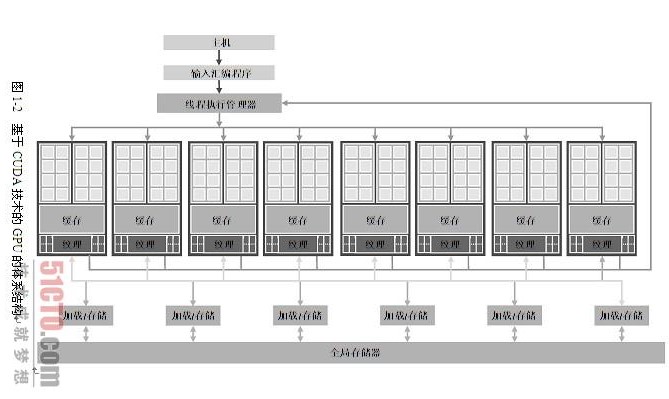

上图是一个基于CUDA技术的典型GPU体系结构。这种体系结构由一个高度线程化的多核流处理器(Streaming Multiprocessor,SM)阵列组成。在上图中,两个多流处理器(Streaming Multiprocessor,SM)形成一个构建块,然而,在基于CUDA技术的GPU的每一代之间,每个构建块中SM的数量可能不同。此外,图中的每个SM又包含多个流处理器(Streaming Processor,SP),它们之间共享控制逻辑和指令缓存。每个GPU都带有若干千兆字节(GB)的 图形双数据速率 (Graphics Double Data Rate,GDDR) DRAM,在上图中称为 全局存储器(global memory)。GPU中的这些GDDR DRAM完全不同于CPU体系中安装在主板上的系统DRAM,它们主要是用于图形处理的帧缓冲区存储器。在图形应用程序中,它们用来保存视频图像和用于3D渲染的纹理信息;而对于计算,它们可以作为带宽芯片外存储器。尽管比典型系统存储器的延迟要长,大规模并行应用程序通常通过高带宽来弥补时延。